Research

Digital Signal Processors

Digital Signal Processors

Zoom

Zoom

Zoom

- Efficient interface design of embedded memory (SRAM) for low power MPEG/H.264 applications

- Low-power MIMO/OFDM baseband processor design

- Design of robot vision processor for supporting multiple camera operations

- Low power image processing design for advanced mobile vision applications

- VLSI implementation of error correction codes (ECC) for high speed PCRAM/DRAM interfaces

- Memory based computation of cryptography processor and physical unclonable function (PUF)

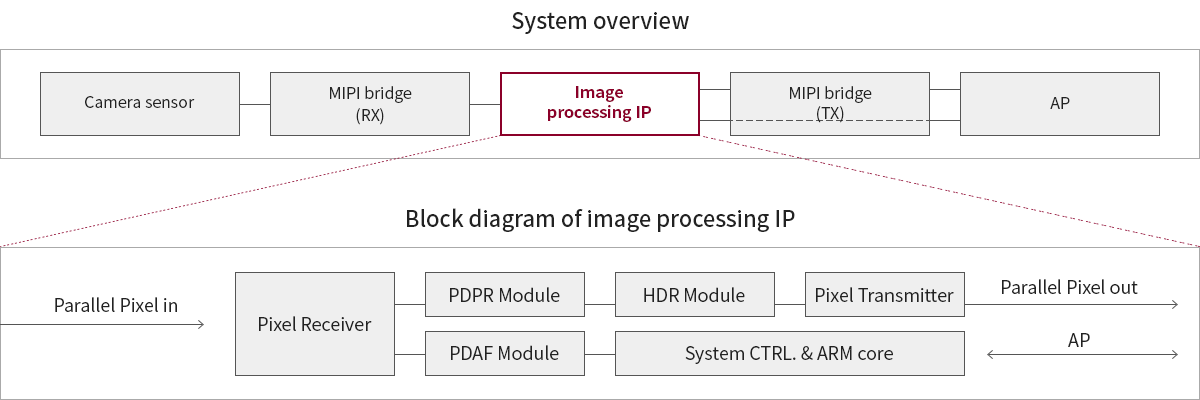

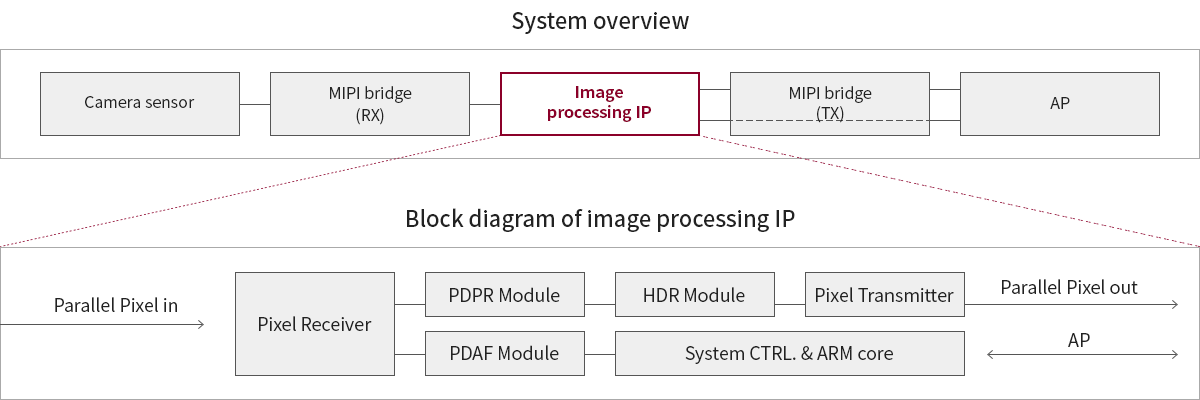

A low power image processing chip : PD/HDR companion ASIC design

Zoom

- MIPI bridge: transferring frame data serially by MIPI CSI-2 format

- Pixel receiver/pixel transmitter: parallel image synchronizer for internal clock & frame size

- Image processing IP:

• PDPR module: performing recovery of PD-pixel

• HDR module: expending pixel range and dynamic tone mapping

• PDAF module: module for automatic focus adjustment - System controller and ARM core: controller of overall system and command receiver from external AP chip

Module functional description

- 16M pixel data(3000 x 5344, raw 10bit)

- Up to 100MHz internal clock

- MIPI CSI-2 interface

- I2C interface

- AXI bus

- Configurable mode initialization through ARM